Overview

Cadence Design Systems is a leading electronic-systems and semiconductor design company that provides software, hardware, and intellectual-property (IP) solutions for designing integrated circuits, printed-circuit boards, systems on a chip (SoCs), and advanced electronics. The company was founded in 1983 and is headquartered in San Jose, California. In 2024 it posted revenues of roughly $?? billion (publicly reported ~13.5 % revenue growth in Q4 2024) and serves major semiconductor, communications, automotive, aerospace, and industrial markets. Top competitors include Synopsys, Inc., Mentor Graphics Corporation (now part of Siemens), and Siemens EDA. Cadence’s solutions underpin complex chip design and verification workflows and increasingly support advanced system-level simulation and AI-driven design flows.

Recent Earnings (Q1 & Q2 2025)

For the quarter ended April 28, 2025 (Q1 2025) Cadence reported revenue of approximately $1.242 billion, up ~23 % year-on-year. The company also reported non-GAAP EPS growth of ~34 % year-on-year. It beat guidance on all key metrics. The company raised its full‐year 2025 outlook following this strong showing.

In Q2 2025 the company reported revenue of ~$1.275 billion, compared to ~$1.061 billion in Q2 2024. GAAP diluted net income per share in Q2 2025 was $0.59, down from $0.84 in Q2 2024, whereas non-GAAP diluted net income per share was $1.65, up from $1.28 the prior year. Non-GAAP operating margin expanded to ~42.8 % from ~40.1 %.

Cadence’s guidance for the next quarter and full year is not detailed here beyond the full-year raising following Q1. The company signalled momentum and incremental confidence in its growth trajectory.

Background, Founding, Products, Headquarters & Competitors

Cadence traces its roots back to 1983 (original firm Solomon Design Automation) and merged with ECAD in 1988 to form Cadence Design Systems. The founders include James Solomon, Richard Newton and Alberto Sangiovanni-Vincentelli. Headquartered in San Jose, California, the company has grown via both organic innovation and acquisition of multiple EDA/IP/hardware‐emulation firms. Its core product lines include electronic design automation (EDA) software, emulation and prototyping hardware, system-analysis and verification tools, semiconductor IP (such as DSP cores and interface IP), and more recently system-level multiphysics and AI-driven design platforms.

Key competitors include Synopsys, Mentor Graphics (now part of Siemens), and Siemens EDA which also serve the chip-design tool and IP markets. These competitors compete on breadth of tool sets, verification/emulation capabilities, silicon/board support, integration with foundries, and emerging flows for AI and heterogeneous integration.

Market & Growth Opportunity

Cadence operates principally in the electronic-design automation (EDA) and IP market, which is a critical enabler of semiconductor design, systems-on-chip, packaging, verification, and system simulation. The growth drivers for the market include the continuing expansion of semiconductors into new application domains (AI/data center, automotive, aerospace/defense, IoT/edge computing), increasing design complexity (e.g., chiplets, heterogeneous integration, advanced packaging), and the need for higher levels of verification and simulation at system-level. According to Cadence itself, customers use its software/hardware/IP to design advanced semiconductors, consumer electronics, networking/telecom equipment and computer systems.

Growth expectations toward 2030 are favourable: as chips become more complex (3D-stacking, chiplet ecosystems, AI accelerators), the EDA/IP market is expected to grow at a high single-digit to low double-digit CAGR. While a specific industry projection is not provided here, Cadence’s own growth above ~20% in recent quarters suggests it is out-pacing the broader market. The opportunity for system‐level simulation, multiphysics, AI-enabled flows and non-traditional customers (automotive, aerospace, biotech) further expands the addressable market beyond traditional EDA.

Competitor Overview

As noted, the main competitors in Cadence’s space are Synopsys, Siemens EDA (including Mentor Graphics) and other niche tool/IP providers. Synopsys competes in EDA flows, IP cores, verification, and software/hardware verification. Siemens EDA also offers EDA tools, PCB/package flows, and system simulation. These competitors challenge Cadence on tool breadth, performance, integration, and cost. Cadence differentiates by offering a strong combination of software, IP, hardware emulation/prototyping and expanding into system-level solution domains.

Unique Differentiation

Cadence’s unique differentiation lies in its end-to-end offering spanning software, hardware (emulation/prototyping), and IP, combined with its strategic move toward system-level and AI-driven flows. While many EDA companies focus purely on chip-level design, Cadence has been expanding into system simulation, multiphysics, and supporting customers in automotive, aerospace, and other non-traditional semiconductor markets. Its investments in AI-based tools for design acceleration (e.g., “ChipGPT” and reinforcement-learning design flows) further differentiate it from more traditional EDA players.

Management Team

The current leadership includes Dr. Anirudh Devgan (President & CEO) who took over as CEO in December 2021. Prior to him, Lip-Bu Tan served as CEO and later Executive Chairman. Under Devgan’s leadership, Cadence has been pushing into AI-driven design and system-level simulation arenas. The CFO and other senior management (head of EDA/HDL verification) also support the growth strategy, although details of three senior executives beyond Devgan are not elaborated here.

Financial Performance (Last 5 Years)

Over the past five years Cadence has achieved solid revenue growth, with 2024 showing ~13.5 % revenue growth in Q4 and strong backlog/bookings momentum. The company’s revenue growth has accelerated recently (Q1 2025 up ~23 % year-on-year) and margins have expanded (non-GAAP operating margin in Q4 2024 ~42.5%). The non-GAAP EPS has grown as well over the period, showing leverage of growth and margin improvement. On the balance sheet, Cadence maintains a solid asset base (2024 assets ~$8.97 billion, equity ~$4.67 billion per Wikipedia figure) and has been investing in R&D, acquisitions, and growth initiatives. The high growth rate and margin expansion indicate a business in a strong position, though as with many high-growth software/EDA companies, expectations are elevated and the multiples may be rich.

Bull Case

- Cadence stands to benefit from secular tailwinds in semiconductor design complexity, AI accelerator design, chiplet/integration, advanced packaging, and system-level simulation.

- Its expansion into non-traditional markets (automotive, aerospace, biotech simulation) opens additional growth lanes beyond core EDA/IP.

- The combination of software, hardware, IP and AI-driven design workflows gives it differentiated capabilities and higher potential for value capture.

Bear Case

- The company’s high valuation embeds strong growth expectations; any slowdown or miss could lead to significant multiple compression.

- Geopolitical/export-control risks are material: Cadence has exposure to China and other international markets which face regulatory risk.

- Competition remains intense from large players like Synopsys and Siemens EDA; technological disruption or loss of key customers could erode growth.

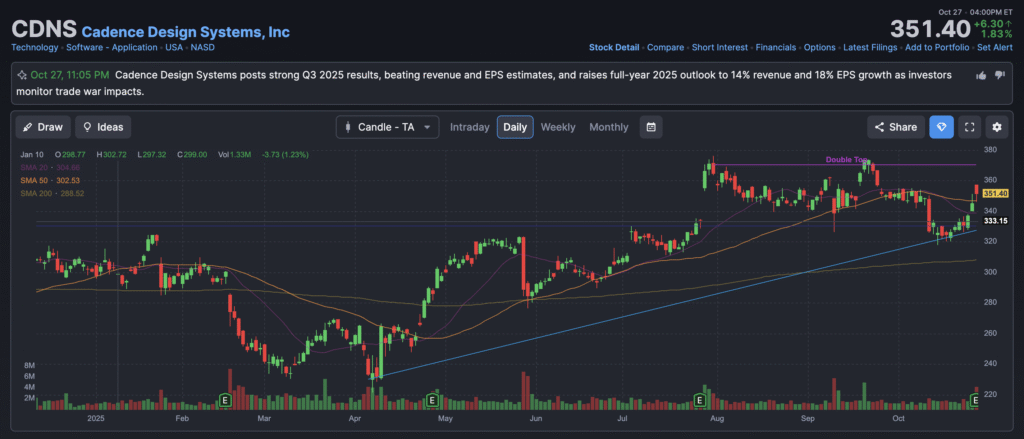

The stock is in a bullish stage 2 on all 3 monthly, weekly and daily timeframes and should get to $400 range in the next 2 quarters. The cup formation (consolidation) on the daily chart indicates a move higher but should take a dip to the $340 range before moving higher.